薄膜沉积是晶圆制造的三大核心步骤之一,薄膜的技术参数直接影响芯片性能。半导体器件的不断缩小对薄膜沉积工艺提出了更高要求,而ALD技术凭借沉积薄膜厚度的高度可控性、优异的均匀性和三维保形性,在半导体先进制程应用领域彰显优势。

由于低温沉积、薄膜纯度以及绝佳覆盖率等固有优点,ALD(原子层淀积)技术早从21世纪初即开始应用于半导体加工制造。DRAM电容的高k介电质沉积率先采用此技术,但近来ALD在其它半导体工艺领域也已发展出愈来愈广泛的应用。

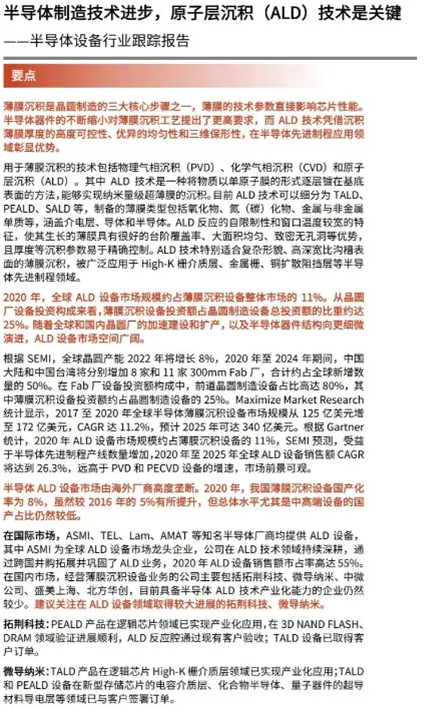

用于薄膜沉积的技术包括物理气相沉积(PVD)、化学气相沉积(CVD)和原子层沉积(ALD)。

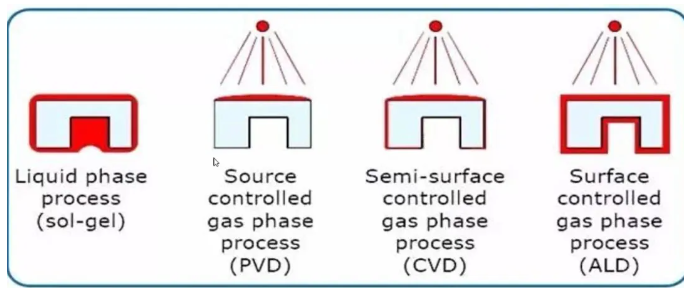

其中ALD是CVD的变种形式,是一种将物质以单原子膜的形式逐层镀在基底表面的方法,将衬底依次暴露到两种活泼的气相化学前驱物中即可形成ALD化合物材料,衬底在特定时间只暴露到一种前驱物中,暴露时间控制得很短,使衬底上仅仅形成一层所吸附前驱物的亚单原子覆盖层。可以通过控制沉积周期次数实现薄膜厚度的精准控制。能够实现纳米量级超薄膜的沉积。

目前ALD技术可以细分为TALD、PEALD、SALD等,制备的薄膜类型包括氧化物、氮(碳)化物、金属与非金属单质等,涵盖介电层、导体和半导体。ALD反应的自限制性和窗口温度较宽的特征,使其生长的薄膜具有很好的台阶覆盖率、大面积均匀、致密无孔洞且厚度等沉积参数易于精确控制。ALD技术特别适合复杂形貌、高深宽比沟槽表面的薄膜沉积,被广泛应用于High-K栅介质层、金属栅、铜扩散阻挡层等半导体先进制程领域。

ALD镀膜的最大优势在于台阶的覆盖性,如下图所示:

金属栅极

利用金属代替多晶硅作为器件的栅极材料,同时金属栅极具有极高的电子密度,可以把极性分子的振动屏蔽掉,提供器件通道内的迁移率,有效解决多晶硅栅极耗尽问题。

金属代替栅极,金属沉积在多晶硅的沟槽里,要求沉积工艺具有良好的台阶覆盖率。

铜互连阻挡层

互连技术常用的工艺主要有Al工艺和Cu工艺,Cu导电性更优良,能够在低温下进行沉积,使用更广泛。Cu最大的缺点是扩散速度很快,容易在电介质内部移动使器件“中毒”,因此镀铜之前必须首先沉积一层防扩散的阻挡层.ALD技术沉积Cu扩散层,高深宽比下,薄膜仍具有良好的均匀性以及防扩散阻挡特性。

微型电容器

ALD在电容器中应用主要包括100nm以下DAM、和嵌入式DRAM等。存储器容量扩大,内部电容器数量剧增,单个电容器尺寸进一步减小,电容器内部沟槽的深宽比越来越大,沉积薄膜的有效面积是器件本身的20倍左右。ALD技术可以满足大面积均匀性,高台阶覆盖率和对膜厚的精确控制。

ALD在半导体领域的应用。随着摩尔定律不断演化,集成电路的特征尺寸及刻蚀沟槽不断微缩,越来越小的刻蚀沟槽给沟槽及其侧壁的镀膜技术带来严苛的挑战,传统PVD及CVD工艺已经无法满足小线宽下良好的台阶覆盖要求。ALD技术具有优良的保型性和均匀性以及较高的台阶覆盖率,开始在半导体产业扮演越来越重要的角色。

Products

研博产品中心

联系人:

销售经理:138 1165 4101

销售经理:136 0112 5769

售后服务:139 1020 6846